|

The 16-bit multiply / divide modes have been tested pretty thoroughly, but the 32/16 may still have some bugs. Sign : out STD_LOGIC - same result checked like for zero, only meaningful for signed operationĭebug : out STD_LOGIC_VECTOR(3 downto 0)) - debug output (leave open) Zero : out STD_LOGIC - quotient is zero (divide) or whole product is zero (multiplication) Ready : out STD_LOGIC - goes high when doneĮrror : out STD_LOGIC - goes high when dividing by 0

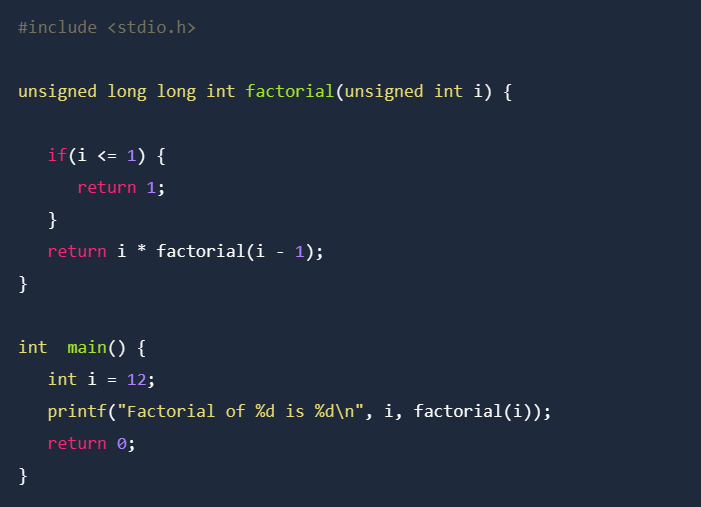

Result : buffer STD_LOGIC_VECTOR (31 downto 0) - 32 bit result when multiplying, when dividing quotient is MSW, remainder is LSW ignored for multiplicationĪrg0h : in STD_LOGIC_VECTOR (15 downto 0) - used as MSW for 32/16 divideĪrg0l : in STD_LOGIC_VECTOR (15 downto 0) - LSW for 32/16 divide, factor0 for 16*16 multiplicationĪrg1 : in STD_LOGIC_VECTOR (15 downto 0) - factor1 for 16*16 multiplication Mode: in STD_LOGIC_VECTOR(1 downto 0) - 00: unsigned multiply, 01: signed multiply, 10: unsigned divide, 11: signed divideĭividend32: in STD_LOGIC - 0: 16/16 divide, 1: 32/16 divide. Start : in STD_LOGIC - Apply high for at least 1 clock cycle to start computation Note that ready will be low as long as reset remains highĬlk : in STD_LOGIC - Clock to drive the FSM Port ( reset : in STD_LOGIC - Active high to initialize. The interface is self-explanatory and should be easy enough to use in various projects: I needed a signed / unsigned multiplier / divider for a different project, and decided to use algorithms described in this book: Yeah, I think I need to write some test code.Implement signed/unsigned 32/16 bit multiplier/divider using a finite state machine (and use it for a fun project) We have maybe 100 calculations to do and 167772 cycles to do them in. Doesn't matter how many steps it takes really. Is this controlling the multiplier to allow it to be used for either signed or unsigned numbers? Unsigned would be great! The subtract input allows me to subtract values without complementing them and the accumulator feedback allows values to be added through sequential load and accumulate steps. These 36 bit numbers are multiplied using the VHDL operator defined in use IEEE.STD_LOGIC_UNSIGNED.ALL Īssigning the result to a 72 bit signal which is then truncated to the 36 lsbs. I see logic that clearly control the sign extension of the 18 bit multiplier inputs to 36 bits.

Initially I had hoped they would be to control if the inputs were complemented to allow for subtraction and such, but they are for controlling the use of the sign bit. The code shows signals named ASIGN and BSIGN. However, I think I may have gleaned a bit of insight from a comprehensive block diagram in the main document combined with the simulation source code for the block in the mode I will be using. The documentation on this DSP unit is truly abysmal lacking much detail at all. It is hard to imagine the multipliers are not signed, but I'm not sure.

Seems that unlike addition, multiplication hardware is different for signed and unsigned numbers. Then someone asked me if these units were signed or unsigned. I was planning to use 18 bit data in Q1.17 format. It also subtracts a 54 bit input from the 55 bit accumulator at the same time. These units accept two 18 bit inputs for the multiplier adding the 36 bit result into the 55 bit accumulator. I'm using the DSP unit (just a fancy name for the multiplier/accumulator unit) of the Gowin GW1N devices to do some fairly simple math.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed